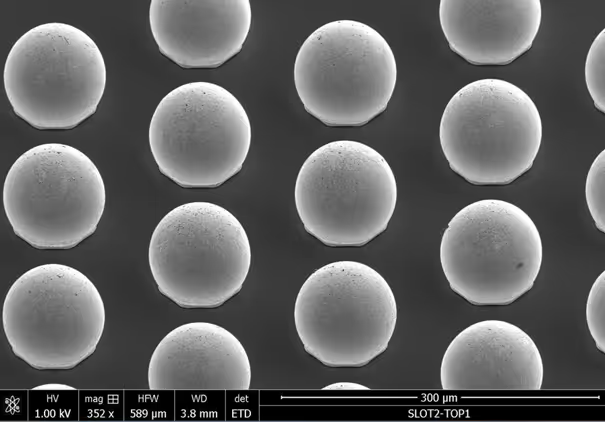

Wafers

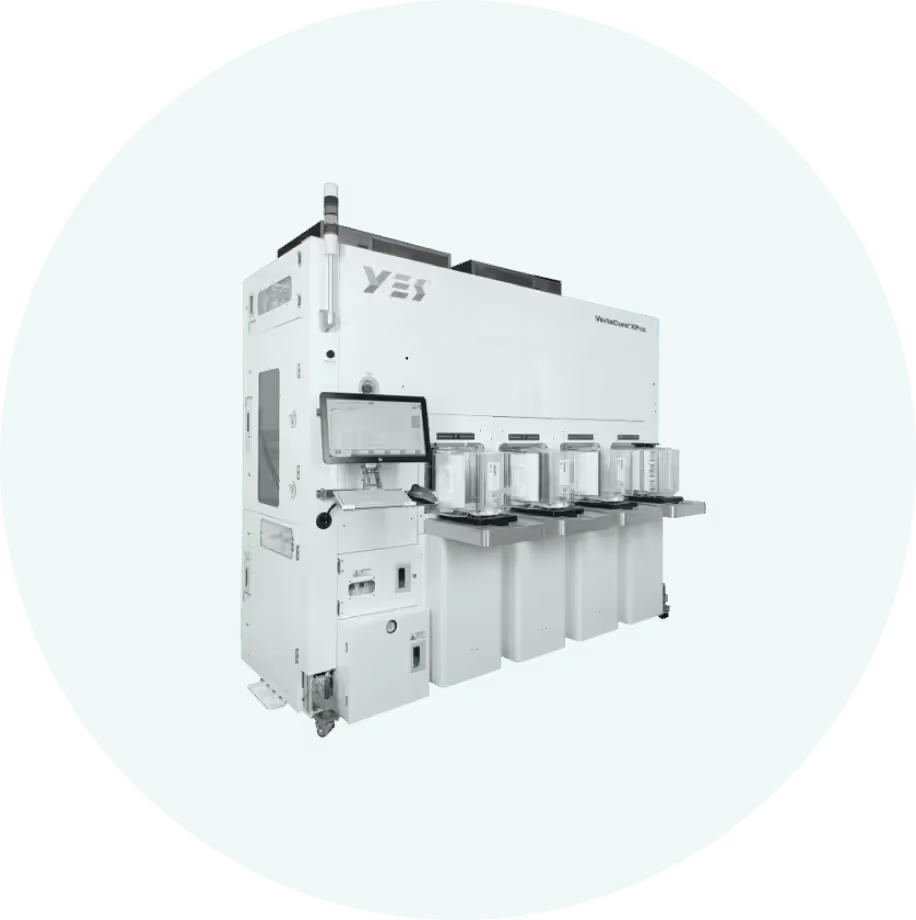

Runs two wafer sizes in parallel in large batch sizes.

Panels

Handles panel dimensions down to 200 μm thickness without breakage.

Copper Eless

Efficient electroless plating of copper for both surface bonding and glass core liner.

Values

.png)

Optimal on-board chemical management

.png)

Specialized handling with panel shock

.png)

Low COO with high throughput

Applications

Via liner

Build-up layers

Interconnects

Glass Etch

Tested on multiple commercially available substrates, the glass core etch can be specified for specific glass needs.

Values

.png)

Specialized glass panel handling

.png)

Optimized chemical usage

.png)

Onboard analysis and metrology

Applications

Through glass via etch

Glass cavity etch for embedded devices

ENEPIG / ENIG

Electroless plating processes for enhanced bonding in advanced packaging.

Values

.png)

Optimal on-board chemical management

.png)

Specialized handling with panel shock

.png)

Low COO with high throughput

Applications

Final layer interface for bonding

Extends package lifetime

Protects copper layers from oxidation

Metal Etch

Metal etch capability for Cu, Ti, TiW, Ru, and more.

Values

.png)

Multiple chemical processes available

.png)

Efficient onboard chemical management

.png)

Chemical cabinets available for bulk chemical delivery

Applications

Seed metal etch

Standard Cleans

Metal etch capability for Cu, Ti, TiW, Ru, and more.

Values

High efficiency processing

.png)

Ultrasonic and megasonic agitation available

.png)

Flexible setup for multiple processes

Applications

Front end particle cleans

-min.avif)